技术篇:晶振外挂负载电容与晶振负载关系

2025-09-05

在电子电路中,晶振是最常见的时钟源之一。为了使晶振正常起振并稳定运行,必须根据其负载电容(Load Capacitance, 简称 CL)合理设计电路中的外挂负载电容。不恰当的电容匹配会导致晶振起振困难、频率偏差增大,甚至系统不稳定。

本文将详细解析晶振负载电容的含义、外挂电容的计算方法,以及电路设计中的实际注意事项。

一、什么是晶振的负载电容(CL)?

晶振厂商在数据手册中通常会标出一个标称负载电容值 CL,比如 18pF、20pF、12pF 等,这代表晶体在该电容负载下被调校以达到其标称振荡频率。

换句话说,只有在等效负载电容 = CL 的情况下,晶振才能输出精确的频率。

二、外挂电容如何影响负载电容?

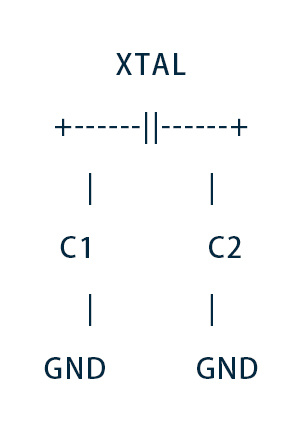

晶振电路常见如下形式:

▪ C1 和 C2 是外挂到地的两个电容(一般是贴片电容);

▪ XTAL 两端分别接至晶振的两个引脚;

▪ 实际上,晶振的等效负载电容 CL 是由 C1 和 C2 通过串联,再考虑 PCB 板和封装引入的寄生电容 Cp 得到的。

三、计算公式:如何根据 CL 推算外挂电容值?

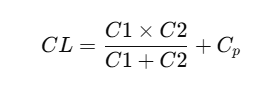

等效负载电容(CL)的公式如下:

其中:

▪ C1、C2:外接到地的电容;

▪ Cp:PCB 板上走线、封装等引入的寄生电容(通常为 2pF ~ 5pF,可通过仿真或经验估算);

▪ CL:晶振 datasheet 中给出的标称负载电容。

【举例说明】

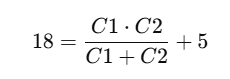

假设晶振规格为 CL = 18pF,PCB 寄生电容 Cp ≈ 5pF,要反推合适的 C1 和 C2:

1.先代入公式:

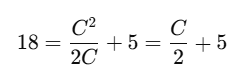

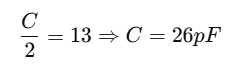

2.假设 C1 = C2 = C,公式简化为:

3.解得:

✅ 所以,推荐外挂电容 C1 = C2 = 27pF(标准值)。

四、为什么外挂电容不匹配会引发问题?

1.频率偏移:如果外挂电容过小或过大,会使晶振偏离其标称频率,造成系统时钟偏差;

2.起振困难或不稳定:负载过重会降低增益,可能导致晶振无法起振或频率抖动;

3.功耗增加:不合适的负载会导致晶振电路能量消耗增加;

4.EMI增加:振荡不稳定时可能产生杂散频率,影响系统电磁兼容性。

五、设计建议与工程实践

1. 认真查看晶振 datasheet

▪ 明确 CL 值;

▪ 明确建议的电路拓扑;

▪ 查是否推荐外挂电容值范围。

2. 考虑实际板子环境

▪ 使用 PCB 仿真或经验估算 Cp;

▪ 若使用高速或精密时钟(如通信系统、MCU主频>100MHz),建议做精确计算或测试。

3. 使用对称电容

▪ 一般建议 C1 = C2,使频率居中、噪声均衡;

▪ 若有特殊匹配需求,也可不对称设计。

4. 调试时可用贴片电容阵列

▪ 可通过贴片电容(如10pF、15pF、22pF、27pF等)试配;

▪ 利用频谱仪或示波器检查输出稳定性和频率准确性。

六、常见问题FAQ

|

问题 |

解答 |

|

若 CL=12pF,外挂电容该选多大? |

假设 Cp=5pF,则 C1=C2≈14pF |

|

为什么有些MCU不要外挂电容? |

有些晶振电路内部已集成负载电容(如STM32),无需外接 |

|

外挂电容不匹配会烧晶振吗? |

通常不会烧坏,但可能起振失败或频率错误 |

结语

晶振的外挂负载电容设计是一个小而关键的细节,直接影响时钟系统的稳定性与准确性。理解 CL 与 C1/C2 之间的计算关系,并根据实际 PCB 寄生电容调整参数,是实现稳定起振和精准频率的关键。

在高速数字系统、通信设备或对时钟要求极高的系统中,合理选择和匹配晶振负载电容是一项必须认真对待的工程任务。

威尼斯有专业的实验室,有多名20年+的应用工程师,可以为客户提供免费的专业匹配测试服务。如果您有这方面需求,请随时与我们销售或技术人员联系。

晶振,晶体振荡器,科普,OCXO,TCXO

上一页

上一页

扫一扫添加微信

扫一扫添加微信